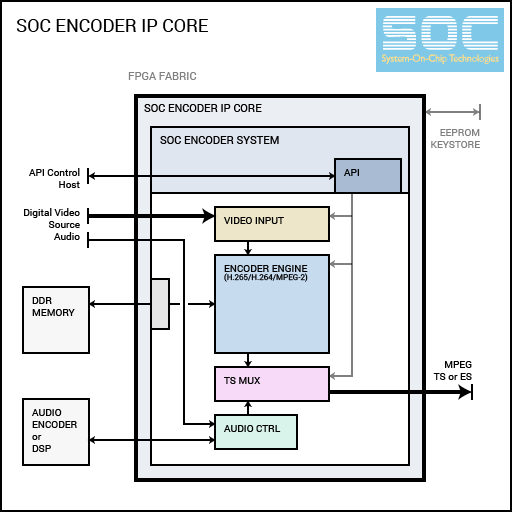

The H.264/AVC HD Video Encoder IP Core is a real-time encoder of HD video or video/audio data. A single core can encode video of up to 1920×1080 resolution at up to 120fps. The latency is 0.25ms and 0.125ms for 30fps and 60fps, respectively - close to "zero latency" between input and output. The core has been optimized to use very few FPGA resources, allowing for a very small footprint and very low power consumption. The incredible efficiency of SOC's IP Cores makes them ideal for power-sensitive electronics and large-scale processing installations.

An intra-only and inter-frame slim versions of the core are available. The intra-only version uses about 1/3 of the logic resources, at the cost of producing about twice the bit rate of the standard version. The inter-frame slim version uses ~1/2 of the full-core resources, allowing it to fit on lower-end devices, or extremely resource-constrained systems. The slim version is perfect for applications with high network bandwidth, where higher bitrates are acceptable. The output bit rate of the slim version is about 20% higher than the standard version.

| Standard: | H.264/AVC (ISO/IEC14496-10) | ||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Resolution/FPS: | Up to FHD(2048 × 1080p) at 60 fps | ||||||||||||||||

| Frame Types: | I, P or B | ||||||||||||||||

| Chroma: | 4:2:0 or 4:2:2 | ||||||||||||||||

| Precision: | 8 or 10 bit | ||||||||||||||||

| Output: | Elementary or Transport Stream | ||||||||||||||||

| Latency: | 0.25 ms | ||||||||||||||||

| Bitrate: |

| ||||||||||||||||

| Entropy Coding: | CAVLC or CABAC | ||||||||||||||||

| FPGA Resources: |

|

The H.264 HD Video Encoder IP Core can be evaluated on SOC's Evaluation Kits. Evaluation kits include a carrier-board with all the ports and extensions needed for most video-based applications. The module and carrier board firmware are reconfigurable, and we can license board files if needed.

Begin the evaluation process through any of these methods: