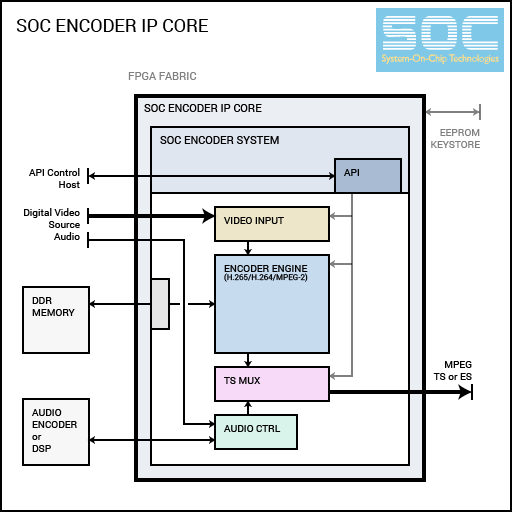

SOC provides an H.264 4K encoder IP Core for Xilinx and Intel FPGAs. The encoder supports up to 4K/60 (4096 × 2160 @60fps) resolution. Parameters are configurable at run-time through API registers.

There are two slimmed-down versions available. The I+P-Frame Slim version uses 50% of standard logic resources, I-Frame-Only Slim version uses only 30% of the standard logic resources. Slim versions are suitable for resource-constrained, low-density FPGAS, if higher bitrates are acceptable.

| Standard: | H.264/AVC (ISO/IEC14496-10) | ||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Resolution/FPS: | Up to 4K(4096 × 2160p) at 60fps | ||||||||||||||||

| Frame Types: | I, P or B | ||||||||||||||||

| Chroma: | 4:2:0 or 4:2:2 | ||||||||||||||||

| Precision: | 8 or 10 bit | ||||||||||||||||

| Output: | Elementary or Transport Stream | ||||||||||||||||

| Latency: | 0.5ms | ||||||||||||||||

| Bitrate: |

| ||||||||||||||||

| Entropy Coding: | CAVLC or CABAC | ||||||||||||||||

| FPGA Resources: |

| ||||||||||||||||

| Note: | Resource values are for 30fps. Double the resource values for 60fps. |

The H.264 4K Video Encoder IP Core can be evaluated on SOC's Evaluation Kits. Evaluation kits include a carrier-board with all the ports and extensions needed for most video-based applications. The module and carrier board firmware are reconfigurable, and we can license board files if needed.

Begin the evaluation process through any of these methods: